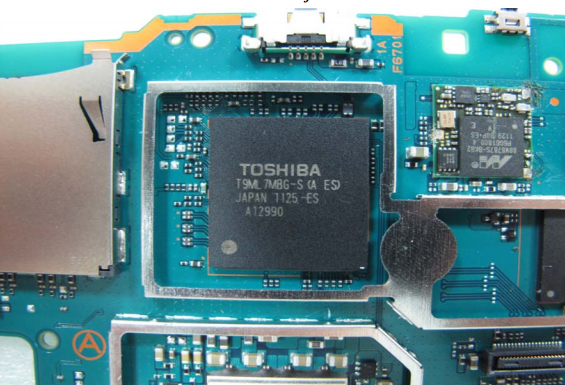

Main Processor

CXD5315GG

The main SoC is labeled CXD5315GG. The design is a stacked SoC with the SDRAM found in the same chip as the processor cores. Toshiba details their "Stacked Chip SOC" on their site.

More information can be found at Chipworks.

According to the internal photos found in the FCC filings, it appears that an earlier version of the chip is labeled T9ML7MBG-S. This does not appear to be a standard model and is likely custom designed in partnership with Sony Computer Entertainment Japan. It is possible that Sony used this service from Toshiba in their design process which is why the prototype demonstrated in the FCC filing shows a Toshiba chip..

Cortex A9 MPcore

The actual application processor cores are Cortex A9, which is common in modern high performance embedded devices like cell phones and tablets. The Technical Reference Manual gives a good overview of the specific processor features and is a good reference for what ARMv7 implementation specific features are enabled. The Vita cores have a MIDR value of 0x412FC09A, meaning it is Cortex A9 r2p10. Indeed there are usage of undocumented CP15 registers.

Another manual that's important is the MPCore Technical Reference Manual which is specific to the multi-core system the Vita uses. The main information of use are descriptors for the private memory region defined with the PERIPHBASE signal. This is mapped to physical address 0x1A000000.

Interrupt Controller

As part of the Cortex A9 MPcore, the Vita also implements the Generic Interrupt Controller Architecture. More information on interrupts can be found here.

PL310 L2 Cache

The Vita uses the PL310 L2 cache is is mapped to 0x1A002000.